مدار منطقی یکی از دروس اصلی مهندسی برق و مهندسی کامپیوتر است که دانشجویان این رشتهها در سالهای نخست دوره کارشناسی باید آن بگذرانند. در این مطلب، مهمترین سرفصلها و موضوعات درس مدار منطقی را معرفی میکنیم که در برنامههای درسی جدید به سیستمهای دیجیتال تغییر نام یافته است.

مدار منطقی چیست ؟

یک مدار منطقی از دو مقدار متفاوت از یک کمیت فیزیکی، معمولاً ولتاژ، برای نشان دادن مقادیر بولی درست (یا ۱) و نادرست (یا ۰) استفاده میکند. مدار منطقی ورودی یا ورودیهایی دارد و دارای یک یا چند خروجی است که حداقل تا حدی به ورودی آنها بستگی دارد. در نمودارهای مدار منطقی ، اتصالات خروجی یک مدار به ورودی مدار دیگر اغلب با نوک پیکان در انتهای ورودی نشان داده میشود.

از نظر عملکردی، مدار منطقی بسیار شبیه توابع یا روشهای برنامهنویسی است. ورودی آن مشابه پارامترهای تابع و خروجیهای آن مشابه مقادیر برگشتی است. با این حال، یک مدار منطقی میتواند چندین خروجی داشته باشد.

دو نوع اصلی مدار منطقی وجود دارد: مدار ترکیبی و مدار حالت. مدارهای ترکیبی مانند یک تابع ساده عمل میکنند. خروجی مدارهای ترکیبی فقط به مقادیر فعلی ورودی آنها بستگی دارد. خروجی مدارهای حالت تنها به ورودیهای آن بستگی ندارد، بلکه به تاریخچه گذشته ورودیهای آن نیز بستگی دارد. به عبارت دیگر، مدار دارای حافظه است. این دو نوع مدار با هم کار میکنند تا «مسیرداده» (Datapath) پردازنده را تشکیل دهند.

جبر بولی و گیتهای منطقی

جبر بولی اساس کل منطق رایانهای است. جبر بولی که در اصل توسط جورج بول، ریاضیدان انگلیسی (۱۸۶۴-۱۸۱۵)، ارائه شد، گزارههایی را توصیف میکند که نتایج آنها درست یا نادرست است. در کار با رایانه، عبارات درست و نادرست با حالت خروجی یک مدار الکترونیکی نشان داده میشود که این حالت میتواند ۱ (درست) یا ۰ (نادرست) باشد.

ما این تغییرات منطقی را به عنوان سطوح ولتاژ درک میکنیم. یعنی وقتی قرار است سطح منطقی نشاندهنده ۱ باشد، ولتاژ خروجی به طور معمول ۵ ولت (یا ولتاژ دیگری) اندازهگیری می شود. برعکس، منطق ۰ با صفر ولت نشان داده میشود. بنابراین، منطق ۱ پنج ولت و منطق ۰ صفر ولت است. البته ذکر این نکته نیز ضروری است که بگویم که ولتاژهای غیر از پنج ولت نیز میتوانند منطق ۱ را نشان دهند و این عدد به مدار و نوع طراحی سیستم بستگی دارد.

عملگرهای اصلی مدار منطقی OR ،AND و NOT هستند. AND ضرب دو گزاره است. یعنی اگر هر دو گزاره درست باشند، این گزاره درست است. اگر هر یک از گزارهها نادرست باشد، این عبارت نادرست است. OR مجموع گزارهها است و اگر هریک از گزارهها درست باشند یا هر دو درست باشند، این گزاره درست است. NOT نیز معکوس یا مکمل یک عبارت است. اگر عبارت درست باشد، مکمل آن نادرست است و بالعکس.

معادلات بولی به صورت جبری جدول زیر بیان میشوند.

| عبارت | گزاره | حکم |

| x AND y | درست | |

| x OR y | درست | |

| NOT x AND NOT y | درست | |

| NOT x OR NOT y |

تابع معکوس یک عملگر منطقی نیز مهم است، زیرا میتوان از آن برای ساده کردن توابع پیچیده استفاده کرد و گاهی تنها راه رسیدن به جواب است. به عنوان مثال، حل معادله زیر تقریباً غیرممکن است:

x OR y, but NOT x AND y

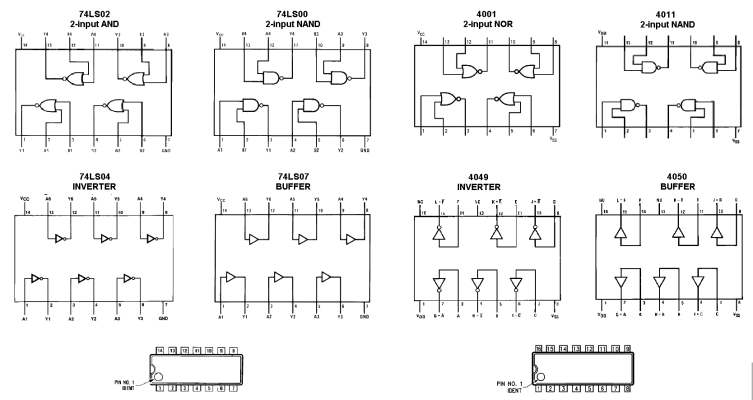

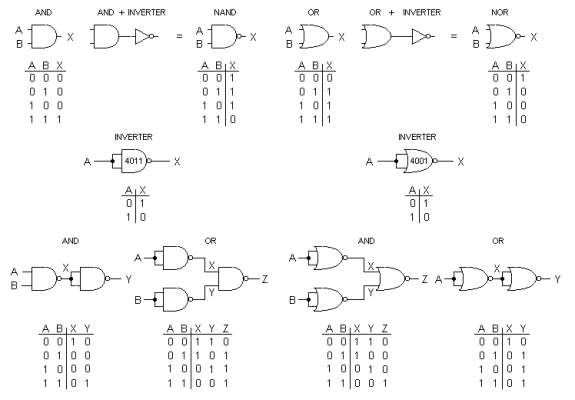

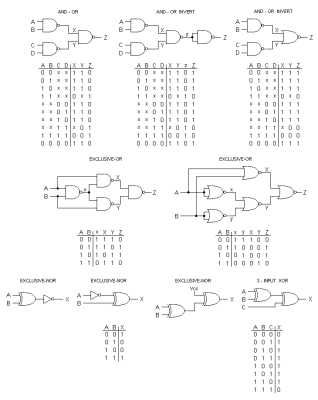

شکل ۱ تراشههای منطقی را که در مدار منطقی استفاده میکنیم و شکل ۲ ساختارهای اولیه آنها را نشان میدهد.

گیتهای منطقی اولیه بر اساس فناوری RTL (منطق مقاومت و ترانزیستور) ساخته شده بود، که تحت تأثیر نویز قرار میگرفت و به طرز آشکاری آزاردهنده و کاملاً کند بود. تکنیکهای ساخت RTL آن زمان نیز انواع گیت را به عملکردهای سادهتر AND ،OR و NOT محدود کرد. با ظهور TTL (منطق ترانزیستور-ترانزیستور) طرحهای پیچیدهتری با موفقیت ساخته شد.

این پیشرفتها شامل چندین ورودی فراتر از چهار گزاره، تریگر لبه پایدار و افزایش گنجایش خروجی بود. اما هیچکدام مهمتر از تغییر پارادایم از منطق مثبت (OR/AND) به منطق منفی (NAND/NOR) نبود (شکل ۳). منطق منفی بسیاری از معادلات بولی را ساده میکند، که منجر به کاهش تعداد گیتها میشود. این امر سبب میشود محاسبات منطقی بسیار پیچیده مانند میکروکنترلرهای تعبیهشده و پردازندهها به راحتی انجام شود.

درک منطق منفی کار سختی نیست، اما برای پیادهسازی مؤثر آن به دقت بیشتری نیاز دارد. دلیل تأکید بر منطق منفی و خوشهبندی انواع گیتها کاهش تعداد آیسی است. بیشتر آیسیهای منطقی حاوی دو یا چند گیت یکسان هستند، اگر ندانید چگونه آنها را برای انجام عملیات مختلف استفاده کنید، بسیاری از آنها ممکن است بدون استفاده بمانند. به عنوان مثال، یک گیت دروازه NAND یا NOR بدون استفاده میتواند به راحتی جایگزین NOT شود، که احتمالاً میتواند IC اضافی را حذف کرده و محصول را کمهزینهتر و قابلاطمینانتر کند.

مسیرداده پردازنده

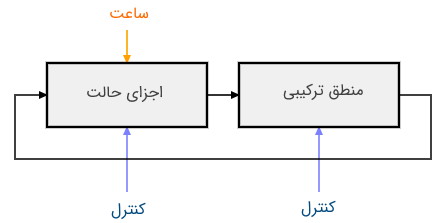

مسیرداده پردازنده از نظر مفهومی به دو قسمت سازماندهی شده است:

- اجزا یا عناصر حالت اطلاعاتی در مورد وضعیت پردازنده در چرخه ساعت فعلی در اختیار دارند. همه ثباتها یا رجیسترها عناصر حالت هستند.

- منطق ترکیبی وضعیت پردازنده را برای چرخه ساعت بعدی تعیین میکند. ALU منطق ترکیبی است.

مدارهای ترکیبی

خروجی مدارهای ترکیبی فقط به مقادیر فعلی ورودی آنها بستگی دارد. مدارهای ترکیبی به طور مفهومی از گیتهای منطقی اساسی ساخته شدهاند: گیت AND، گیت OR، گیت NOT و… . خروجی گیتها در مدارهای ترکیبی هرگز مستقیماً به ورودیهای قبلی بازگردانده نمیشود.

گیتهای منطقی اساسی را میتوان با هم ترکیب کرد و انواع واحدهای سطوح بالاتر را تشکیل داد: مسیریابی و محاسباتی.

مسیریابی

- مالتیپلکسرها: دارای چندین سیگنال ورودی داده و یک ورودی کنترل هستند. خروجی با یکی از ورودیها یکسان است. مقدار سیگنال کنترل تعیین می کند که کدام یک باشد.

- دیمالتیپلکسرها: یک سیگنال ورودی داده، یک ورودی کنترل و چندین سیگنال خروجی دارند. همه سیگنالهای خروجی ۰ هستند (نادرست) به جز سیگنالی که توسط ورودی کنترل انتخاب شده است. خروجی انتخابشده مشابه ورودی داده است.

محاسباتی

- جمعکنندههای کامل: یک جمع ستونی باینری را انجام میدهند. اینها بلوکهای اصلی اولیه برای جمع و تفریق چندبیتی هستند.

- جمعکنندهها و تفریقکنندهها: دو عدد باینری را جمع یا تفریق میکنند. یک تفریقکننده همان یک جمعکننده با مدارهای اضافی است که عمل مکمل را در یکی از ورودیها انجام دهد. این مدارها معمولاً طوری طراحی شدهاند که علاوه بر جمع یا تفریق مطابق سیگنال کنترلی عمل کنند.

- مقایسهکننده: دو عدد باینری یا مکمل را مقایسه میکند.

مدار حالت

در ادامه مدارهای حالت فیلپفلاپ و رجیستر را معرفی میکنیم.

فیلپفلاپ

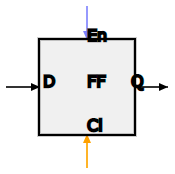

فلیپ فلاپ عنصر اساسی مدار حالت و دارای سه ورودی است:

- D – دادههایی که باید در فلیپفلاپ نوشته شوند.

- En – امکان میدهد دادهها در فلیپفلاپ نوشته شوند.

- Cl – کلاک (ساعت) که تعیین میکند چه زمانی دادهها در فلیپفلاپ نوشته شوند.

یک فلیپفلاپ دارای یک خروجی است:

- Q – جدیدترین مقدار داده که در فلیپفلاپ نوشته شده است.

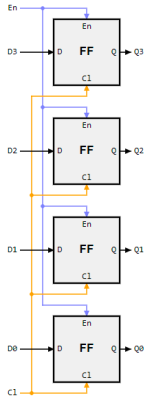

رجیستر

رجیستر یا ثبات نسخه آنالوگ چندبیتی فلیپفلاپ است که دارای سه ورودی است:

- D – دادههایی که باید در رجیستر ثبت شوند.

- En – امکان میدهد دادهها در رجیستر ثبت شوند.

- Cl – که تعیین میکند چه زمانی دادهها در رجیستر ثبت شوند.

یک رجیستر دارای یک خروجی است:

- Q – جدیدترین مقدار داده که در رجیستر نوشته شده است.

اینها همان ورودیها و خروجیهایی هستند که یک فلیپفلاپ دارد. تنها تفاوت این است که ورودی D و خروجی Q سیگنالهای چندبیتی هستند. همانطور که در شکل بالا نشان داده شده است، یک رجیستر به عنوان گروهی از فلیپ فلاپ ها اجرا می شود که ساعت خود را به اشتراک می گذارند و سیگنال ها را فعال می کنند.

+ در ریسمونک بخوانید: